# **DM164**

**Version** : A.003 **Issue Date** : 2011/05/18

File Name : SP-DM164-A.03.doc

Total Pages : 31

# 8x3-CHANNEL CONSTANT CURRENT LED DRIVER

9-7F-1, Prosperity Road I, Science Based Industrial Park, Hsin-Chu, Taiwan 300, R.O.C.

Tel: 886-3-5645656 Fax: 886-3-5645626

### **DM164**

### 8x3-CHANNEL CONSTANT CURRENT LED DRIVERS

### **General Description**

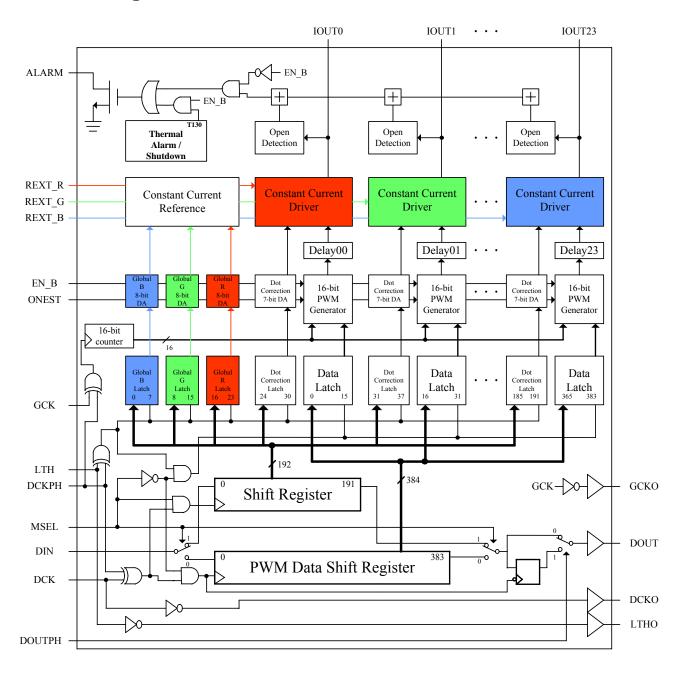

The DM164 is a LED current sink driver incorporating independent shift registers and data latches for grayscale PWM data (GD mode\*1) and current adjustment data (D&G mode\*1), 8x3-channels constant current circuitry with current value set by 3 external resistors, 65,536 grayscale PWM function unit, 128 levels current adjustment for each channel and 256 levels global brightness control (White balance). Each channel provides maximum current of 90mA. The DM164 also supports the LED open detection capability, thermal alarm and shutdown function. There are two methods to communicate error signals to the system. One is through serial output data to indicate which channel has failure. The other is by means of dedicated Alarm pin.

### **Features**

- Constant current outputs with current value set by 3 external resistors.

- Max PWM clock frequency

Cascade: 36MHz@VDD=3.3V(Refresh rate = 550Hz), 40MHz@VDD=5V (610Hz)

- Max data clock frequency

- Cascade: 30MHz@VDD=3.3V, 35MHz@VDD=5V

- Maximum output current: 90mA

- Maximum output voltage: 17V

- ◆ 16-bit grayscale for each LED

- ◆ 8-bit current adjustment for global brightness control (White Balance)

- 7-bit current adjustment for each LED (Dot Correction)

- Supply Voltage: 3V to 5.5V

- ◆ LED Open Detection

- Thermal Alarm and Shutdown

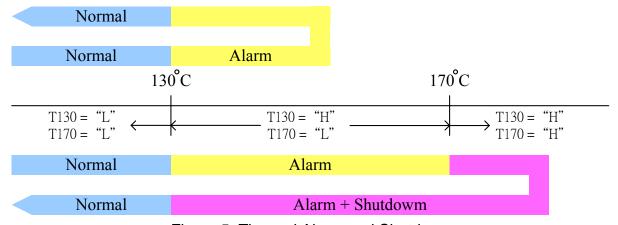

Alarm (junction temperature >130°C) Shutdown (junction temperature > 170°C)

- ♦ One-Shot Option

- ◆ Built-in Buffer for Data, PWM Clock, Latch signal and Data Clock

- Average Separate IOUT PWM Waveform Option

## **Package**

LQFP48 (7mmX7mm), QFN48 (7mmX7mm)

<sup>\*1:</sup> See Page 10

# **Block Diagram**

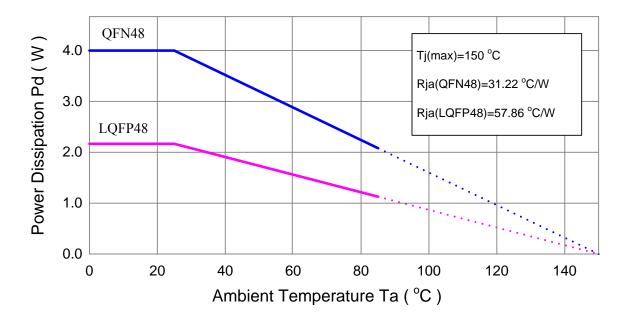

### **DISSIPATION RATINGS**

| PACKAGE | POWER DISSIPATION<br>(Tj_max=150 °C) | THERMAL RESISTANCE (Rja, Ta=25°C) |

|---------|--------------------------------------|-----------------------------------|

| QFN48   | 4.00 W                               | 31.22 °C/W                        |

| LQFP48  | 2.16 W                               | 57.86 °C/W                        |

# **Pin Description**

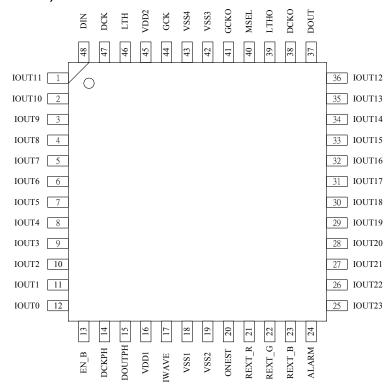

### LQFP48 (Top View)

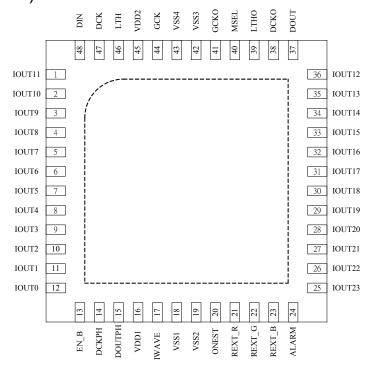

## QFN48 (Top View)

| PIN NAME  | FUNCTION                                                                                                                                                                                | QFN48 / LQFP48    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|           |                                                                                                                                                                                         | pin number        |

| VDD1,VDD2 | Power supply terminal.                                                                                                                                                                  | 16,45             |

| VSS1~4    | Ground terminal.                                                                                                                                                                        | 18,19,42,43       |

|           | External resistor connected between Rext and GND                                                                                                                                        |                   |

| Rext_R    | for driver current setting.                                                                                                                                                             | 21                |

| _         | REXT_R controls outputs:                                                                                                                                                                |                   |

| Rext_G    | IOUT0, 3, 6, 9, 12, 15, 18, 21.  REXT_G controls outputs:                                                                                                                               | 22                |

|           | IOUT1, 4, 7, 10, 13, 16, 19, 22.                                                                                                                                                        |                   |

| Rext_B    | REXT_B controls outputs:                                                                                                                                                                | 23                |

|           | IOUT2, 5, 8, 11, 14, 17, 20, 23.                                                                                                                                                        |                   |

|           | 10012, 0, 0, 11, 11, 17, 20, 20.                                                                                                                                                        | 12,11,10,9,8,7,   |

| IOUT0~11  | LED driver outputs.                                                                                                                                                                     | 6,5,4,3,2,1       |

|           |                                                                                                                                                                                         | 36,35,34,33,32,31 |

| IOUT12~23 | LED driver outputs.                                                                                                                                                                     | 30,29,28,27,26,25 |

| DIN       | Serial input for grayscale PWM data and current                                                                                                                                         | 48                |

| אווע      | adjustment data.                                                                                                                                                                        | 40                |

| DOUT      | Serial output for grayscale PWM data and current adjustment data.                                                                                                                       | 37                |

| DCK       | Synchronous clock input for serial data transfer. The input data of DIN can be transferred at either the rising edges of DCK or the falling edges of DCK depending on the signal DCKPH. | 47                |

| DCKO      | Synchronous clock output for serial data transfer. <b>DCKO</b> = DCK.                                                                                                                   | 38                |

|           | When DCKPH = L, input data is shifted in by rising                                                                                                                                      |                   |

|           | edge of DCK,                                                                                                                                                                            |                   |

| DCKPH     | When DCKPH = H, input data is shifted in by falling edge of DCK                                                                                                                         | 14                |

|           | When DOUTPH = H, DOUT is shifted out with half                                                                                                                                          |                   |

| DOUTPH    | DCK cycle delay                                                                                                                                                                         | 15                |

|           | When DOUTPH = L, DOUT is shifted out without delay                                                                                                                                      |                   |

|           | Data latch input pin.                                                                                                                                                                   |                   |

| <b>.</b>  | When DCKPH=L & LTH=H or DCKPH=H & LTH=L, internal latches become transparent and PWM counter                                                                                            |                   |

| LTH       | value will be set to FFFF(h).                                                                                                                                                           | 46                |

|           | When DCKPH=L & LTH=L or DCKPH=H & LTH=H, internal latches hold data.                                                                                                                    |                   |

| LTHO      | Data latch output pin. <b>LTHO=</b> TTH                                                                                                                                                 | 39                |

| 0.014     | Clock input for PWM operation. When DCKPH=L                                                                                                                                             |                   |

| GCK       | (DCKPH=H), the internal PWM counter will count up with rising (falling) edge of GCK.                                                                                                    | 44                |

|           | 5 \ 5, 5                                                                                                                                                                                |                   |

| GCKO  | Clock output. <b>GCKO=</b> GCK                                                                                                                                                                         | 41 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| EN_B  | Blank all outputs.  When EN_B = H, all outputs are forced OFF.  When EN_B = L, all outputs are controlled by grayscale PWM control.                                                                    | 13 |

| MSEL  | When MSEL = H, the device is operated in Dot Correction Data & Global Brightness Control Data Input Mode (D&G mode). When MSEL = L, the device is operated in Grayscale PWM Data Input Mode (GD mode). | 40 |

| ALARM | Output open drain terminal for an alarm function. when EN_B = L, It will go low as LED open when EN_B = H, It will go low as chip overheated.                                                          | 24 |

| IWAVE | When IWAVE = H, traditional lout waveform. When IWAVE = L, average separate lout waveform.                                                                                                             | 17 |

| ONEST | When ONEST = H, one-shot function is enabled. When ONEST = L, one-shot function is disabled.                                                                                                           | 20 |

### Maximum Ratings (Ta=25°C, Tj(max) = 150°C)

| CHARACTERISTIC        | SYMBOL   |                                 | RATING    |                         |            |          |                        |

|-----------------------|----------|---------------------------------|-----------|-------------------------|------------|----------|------------------------|

| Supply Voltage        | Vdd      |                                 |           | -0.3 ~ 7.0              | )          |          | V                      |

| Input Voltage         | VIN      |                                 | -(        | 0.3 ~ V <sub>DD</sub> + | 0.3        |          | V                      |

| Output Current        | lout     |                                 |           | 90                      |            |          | mA                     |

| Output Voltage        | Vout     |                                 |           | -0.3 ~ 17               | •          |          | V                      |

| DCK Frequency         | FDCK     | Cascade Vdd=5V 35 Vdd=3.3V 30   |           |                         |            |          | MHz                    |

| GCK Frequency         | FGCK     | Cascade                         | Vdd=5V    | 40                      | Vdd=3.3V   | 36       | MHz                    |

| GND Terminal Current  | IGND     |                                 |           | 2200                    |            |          | mA                     |

| Power Dissipation     | PD       | 4.                              | 00 ( QFN4 | l8); 2.16 (L            | _QFP48) (1 | Га=25°С) | W                      |

| Thermal Resistance    | Rth(j-a) | 31.22 ( QFN48 ); 57.86 (LQFP48) |           |                         |            |          | %C\M                   |

| Operating Temperature | Тор      | -40 ~ 85                        |           |                         |            |          | $^{\circ}\!\mathbb{C}$ |

| Storage Temperature   | Tstg     |                                 |           | -55 ~ 150               | )          |          | $^{\circ}\!\mathbb{C}$ |

# **Recommended Operating Condition**

### DC Characteristics (Ta = 25°C)

| CHARACTERISTIC | SYMBOL | CONDITION   | MIN.         | TYP. | MAX.                 | UNIT |

|----------------|--------|-------------|--------------|------|----------------------|------|

| Supply Voltage | VDD    | _           | 3            |      | 5.5                  | V    |

| Output Voltage | Vout   | <del></del> |              | _    | 17                   | V    |

|                | Ю      | OUTn        |              |      | 90                   |      |

| Output Current | Іон    | SERIAL-OUT  |              |      |                      | mA   |

| •              | lol    | SERIAL-OUT  |              |      |                      |      |

| Input Voltage  | VIH    | <u> </u>    | $0.7 V_{DD}$ |      | V <sub>DD</sub> +0.2 | V    |

| VIL | _ | -0.2 | _ | 0.3 V <sub>DD</sub> |  |

|-----|---|------|---|---------------------|--|

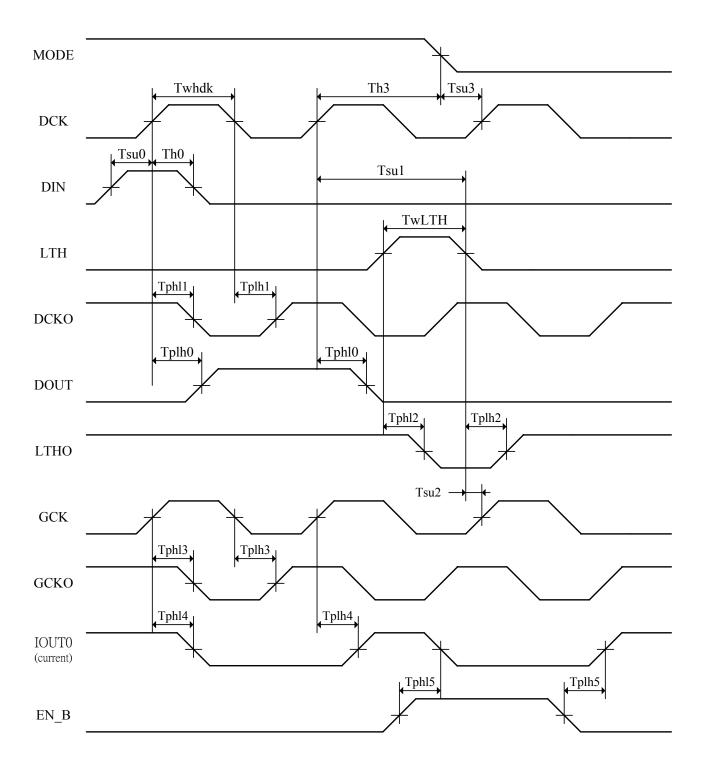

### AC Characteristics ( $V_{DD} = 5.0 \text{ V}$ , Ta = 25°C, REXT = 3.9k $\Omega$ )

| CHARACTERISTIC       | SYMBOL        | CONDITION               | MIN. | TYP. | MAX. | UNIT |

|----------------------|---------------|-------------------------|------|------|------|------|

| DCK Frequency        | FDCK          | Cascade operation       | _    | _    | 35   | MHz  |

| DCK pulse duration   | Twhdk / Twldk | High or low level       | _    | 13   | _    | ns   |

| DCK rise/fall time   | Trdk/ Tfdk    | Single, CLoad=13pF      | _    | 5    |      | ns   |

| GCK Frequency        | FGCK          | Cascade operation       | _    |      | 40   | MHz  |

| GCK pulse duration   | Twhgk / Twlgk | High or low level       | _    | 12   |      | ns   |

| GCK rise/fall time   | Trgk/ Tfgk    | Single, CLoad=13pF      | _    | 5    | _    | ns   |

| Set-up Time for DIN  | Tsu0          | Before DCK rising edge  | _    | 10   | _    | ns   |

| Hold Time for DIN    | Th0           | After DCK rising edge   | _    | 10   | _    | ns   |

| Set-up Time for DCK  | Tsu1          | Before LTH falling edge | _    | 30   | _    | ns   |

| LTH Pulse Width      | TwLTH         | _                       | _    | 15   | _    | ns   |

| Set-up Time for LTH  | Tsu2          | Before GCK rising edge  | _    | 10   | _    | ns   |

| Set-up Time for MSEL | Tsu3          | Before DCK rising edge  | _    | 10   | _    | ns   |

| Hold Time for MSEL   | Th3           | After DCK rising edge   | _    | 30   |      | ns   |

### AC Characteristics ( $V_{DD} = 3.3 \text{ V}$ , Ta = 25°C, REXT = 3.9k $\Omega$ )

| CHARACTERISTIC       | SYMBOL        | CONDITION               | MIN. | TYP. | MAX. | UNIT |

|----------------------|---------------|-------------------------|------|------|------|------|

| DCK Frequency        | FDCK          | Cascade operation       | _    | _    | 30   | MHz  |

| DCK pulse duration   | Twhdk / Twldk | High or low level       | _    | 15   | _    | ns   |

| DCK rise/fall time   | Trdk/ Tfdk    | Single, CLoad=13pF      | _    | 4    | _    | ns   |

| GCK Frequency        | FGCK          | Cascade operation       | _    | _    | 36   | MHz  |

| GCK pulse duration   | Twhgk / Twlgk | High or low level       | _    | 13   | _    | ns   |

| GCK rise/fall time   | Trgk/ Tfgk    | Single, CLoad=13pF      | _    | 4    | _    | ns   |

| Set-up Time for DIN  | Tsu0          | Before DCK rising edge  | _    | 10   | _    | ns   |

| Hold Time for DIN    | Th0           | After DCK rising edge   | _    | 10   | _    | ns   |

| Set-up Time for DCK  | Tsu1          | Before LTH falling edge | _    | 30   | _    | ns   |

| LTH Pulse Width      | TwLTH         |                         | _    | 15   | _    | ns   |

| Set-up Time for LTH  | Tsu2          | Before GCK rising edge  | _    | 10   | _    | ns   |

| Set-up Time for MSEL | Tsu3          | Before DCK rising edge  |      | 10   | _    | ns   |

| Hold Time for MSEL   | Th3           | After DCK rising edge   | _    | 30   | _    | ns   |

See Page 9: Timing Diagram

# Electrical Characteristics (V<sub>DD</sub> = 5.0 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC              | SYMBOL       | CONDITIO            | N            | MIN.         | TYP.  | MAX.                | UNIT   |

|-----------------------------|--------------|---------------------|--------------|--------------|-------|---------------------|--------|

| Input Voltage "H" Level     | VIH          | _                   |              | $0.7~V_{DD}$ |       | $V_{DD}$            | V      |

| Input Voltage "L" Level     | VIL          | _                   |              | GND          |       | 0.3 V <sub>DD</sub> | V      |

| Output Leakage Current      | lleak        | Vout = 17 V         |              | _            |       | ± 0.1               | uA     |

| Output Voltage ( DOUT)      | Vol          | IOL = 2 mA          |              |              |       |                     | V      |

|                             | Voн          | IOH = -2 mA         |              |              |       | _                   | V      |

| Output Current              | IOL1         | Vout = 1.0V         |              |              | ± 1   | ± 3                 | %      |

| (Channel-Channel)           | IOLI         | $REXT = 3.9k\Omega$ |              |              | -1    | ± 3                 | 70     |

| Output Current              | loi 3        | Vout = 1.0V         |              |              |       | ± 6                 | %      |

| (Chip-Chip)                 | IOL3         | $REXT = 3.9k\Omega$ |              |              |       | ± 0                 | /0     |

| Output Voltage              | % / Vout     | $REXT = 3.9k\Omega$ |              |              | ± 0.1 | ± 0.5               | % / V  |

| Regulation                  | 70 / V Out   | Vout = 1.0~3.0V     |              |              | ± 0.1 | ± 0.0               | 70 / V |

|                             |              | VDD=5.0V, $REXT=3$  | 3.9kΩ        |              | 13    |                     |        |

|                             | IDD analan   | , REXT = 1          | .4k $\Omega$ |              | 34    |                     |        |

| Supply Current <sup>1</sup> | IDD, analog  | VDD=3.3V, $REXT=3$  | 3.9kΩ        |              | 12    |                     | m ∧    |

| Supply Current <sup>1</sup> |              | , REXT = 1          | .4k $\Omega$ |              | 33    |                     | mA     |

|                             | IDD, digital | Cload=2pF,          | VDD=5.0V     |              | 2.4   |                     |        |

|                             | טטו, uigitai | DCK=GCK=10MHz       | VDD=3.3V     |              | 1.8   |                     |        |

# Switching Characteristics (V<sub>DD</sub> = 5.0V, Ta = 25°C)

|                | ,              | ,                                           |      |      |      |      |

|----------------|----------------|---------------------------------------------|------|------|------|------|

| CHARACTERISTIC | SYMBOL         | CONDITION                                   | MIN. | TYP. | MAX. | UNIT |

| DOUT Rise time | t <sub>r</sub> | VIH=VDD<br>VIL=GND                          | _    | 5    | 10   | ns   |

| DOUT Fall time | t <sub>f</sub> | REXT=3.9k $\Omega$<br>CL=13pF               |      | 5    | 10   | ns   |

| IOUT Rise time | t <sub>r</sub> | VIH=VDD, VIL=GND<br>REXT=3.9kΩ              |      | 8    | 30   | ns   |

| IOUT Fall time | t <sub>f</sub> | VLED=5.0V<br>RL=100Ω, CL=33pF<br>10% to 80% |      | 8    | 30   | ns   |

| DOUT             | Tplh0 | After DCK rising edge   | _ | 28 | _ | ns |

|------------------|-------|-------------------------|---|----|---|----|

| DOUT             | Tphl0 | After DCK rising edge   | _ | 28 | _ | ns |

| DCKO             | Tplh1 | After DCK falling edge  | _ | 14 | _ | ns |

| DCKO             | Tphl1 | After DCK rising edge   | _ | 17 | _ | ns |

| LTHO             | Tplh2 | After LTH falling edge  | _ | 14 | _ | ns |

| LTHO             | Tphl2 | After LTH rising edge   | _ | 17 | _ | ns |

| GCKO             | Tplh3 | After GCK falling edge  | _ | 16 | _ | ns |

| GCKO             | Tphl3 | After GCK rising edge   | _ | 16 | _ | ns |

| IOUT0 (turn on)  | Tplh4 | After GCK rising edge   | _ | 30 | _ | ns |

| IOUT0 (turn off) | Tphl4 | After GCK rising edge   | _ | 31 | _ | ns |

| IOUT0 (turn on)  | Tplh5 | After EN_B falling edge | _ | 27 | _ | ns |

| IOUT0 (turn off) | Tphl5 | After EN_B rising edge  | _ | 25 | _ | ns |

# Switching Characteristics ( $V_{DD} = 3.3V$ , Ta = 25°C)

|                |                | i e                                         | ı    |      |      | 1    |

|----------------|----------------|---------------------------------------------|------|------|------|------|

| CHARACTERISTIC | SYMBOL         | CONDITION                                   | MIN. | TYP. | MAX. | UNIT |

| DOUT Rise time | t <sub>r</sub> | VIH=VDD<br>VIL=GND                          |      | 4    | 10   | ns   |

| DOUT Fall time | t <sub>f</sub> | REXT=3.9k $\Omega$<br>CL=13pF               |      | 4    | 10   | ns   |

| IOUT Rise time | t <sub>r</sub> | VIH=VDD, VIL=GND<br>REXT=3.9kΩ<br>VLED=5.0V | _    | 12   | 30   | ns   |

| IOUT Fall time | t <sub>f</sub> | RL=100Ω, CL=33pF<br>10% to 80%              |      | 12   | 30   | ns   |

| DOUT             | Tplh0 | After DCK rising edge   | _ | 35 | _ | ns |

|------------------|-------|-------------------------|---|----|---|----|

| DOUT             | Tphl0 | After DCK rising edge   | _ | 35 | _ | ns |

| DCKO             | Tplh1 | After DCK falling edge  | _ | 21 | _ | ns |

| DCKO             | Tphl1 | After DCK rising edge   | _ | 19 | _ | ns |

| LTHO             | Tplh2 | After LTH falling edge  | _ | 20 | _ | ns |

| LTHO             | Tphl2 | After LTH rising edge   | _ | 20 | _ | ns |

| GCKO             | Tplh3 | After GCK falling edge  | _ | 23 | _ | ns |

| GCKO             | Tphl3 | After GCK rising edge   | _ | 23 | _ | ns |

| IOUT0 (turn on)  | Tplh4 | After GCK rising edge   | _ | 42 | _ | ns |

| IOUT0 (turn off) | Tphl4 | After GCK rising edge   | _ | 41 | _ | ns |

| IOUT0 (turn on)  | Tplh5 | After EN_B falling edge | _ | 39 | _ | ns |

| IOUT0 (turn off) | Tphl5 | After EN_B rising edge  | _ | 33 | _ | ns |

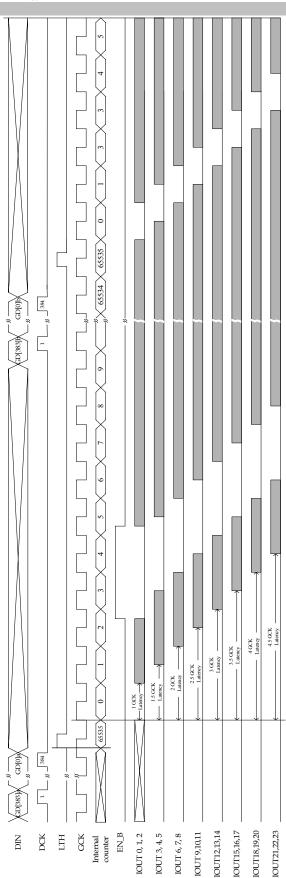

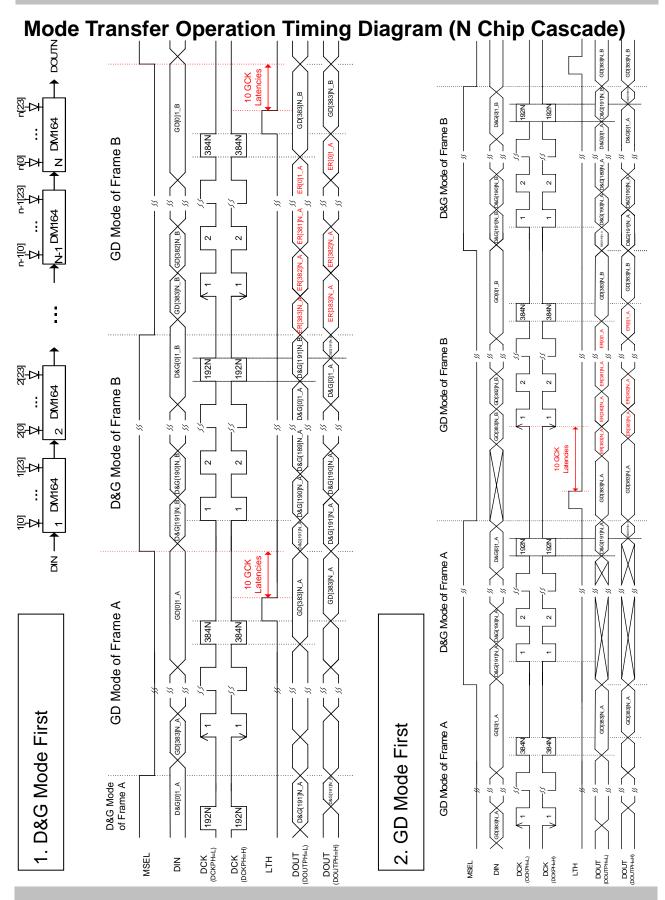

# **Timing Diagram**

### Serial Data Interface

The DM164 includes a flexible data transfer interface. The data can be transferred from DIN pin to the shift registers at either the rising edge of DCK or the falling edge of DCK depending on the signal DCKPH. After all data are clocked in, a high level LTH signal can transfer the serial data to the data latches (Level Sensitive). The serial data format can be 192-bit or 384-bit wide, depending on the operating mode of the device.

# **Operating Modes**

The DM164 has two operating modes depending on the signal MSEL. Table 1 shows the available operating modes. When MSEL = H, the device operates at the D&G mode. D&G mode is used to set dot correction data and global brightness control data after IC power up or any time. When MSEL = L, the device becomes GD mode. GD mode is used to set grayscale PWM data after D&G mode.

MSEL MODE SHIFT REGISTER

H Dot Correction Data & Global Brightness Control

Data Input Mode (D&G mode)

L Grayscale PWM Data Input Mode (GD mode)

384-bit

Table 1. Two Operating Modes

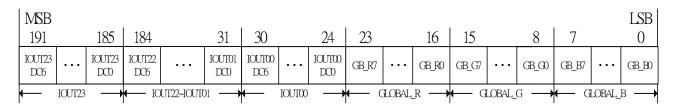

### **D&G Mode Data Format**

At D&G mode, dot correction data of all channels and global brightness control data of different colors are transferred into the chip at the same time. The complete dot correction data format consists of 24 x 7-bit and the global brightness control data of three different colors consists of 3 x 8-bit. The total shift registers width at D&G mode is 192-bit. All data is clocked in with MSB first. Figure 1 shows the D&G mode data format.

Figure 1. D&G Mode Data Format (D&G[191:0])

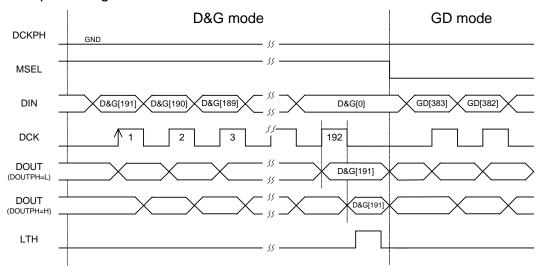

To operate the DM164 in D&G mode, MSEL must be set to high. The shift register width is

then set to 192-bit wide. The input data can be transferred at either the rising edge of DCK or the falling edge of DCK by setting DCKPH to L or H. After all data are transferred into the D&G mode shift registers, the D&G mode data can be latched from shift registers to the data latches by a LTH signal at either D&G mode or GD mode. Figure 2 shows the D&G mode data input timing chart.

Figure 2. D&G Mode Data Input Timing Chart

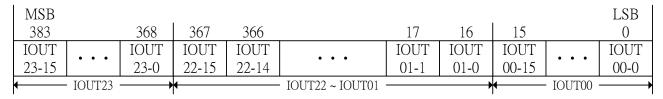

### **GD Mode Data Format**

At GD mode, the grayscale PWM data will be transferred to the shift registers. The complete grayscale PWM data format consists of 24 x 16-bit. The total shift registers width at GD mode is 384-bit. All grayscale PWM data is clocked in with MSB first. Figure 3 shows the GD mode data format.

Figure 3. GD Mode Data Format (GD[383:0])

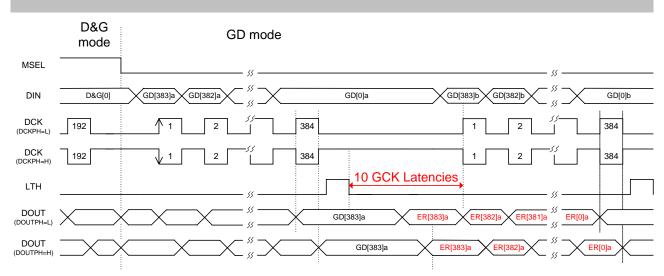

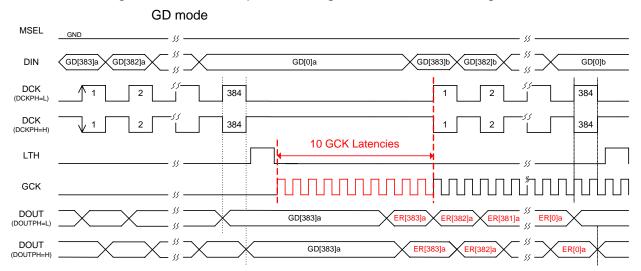

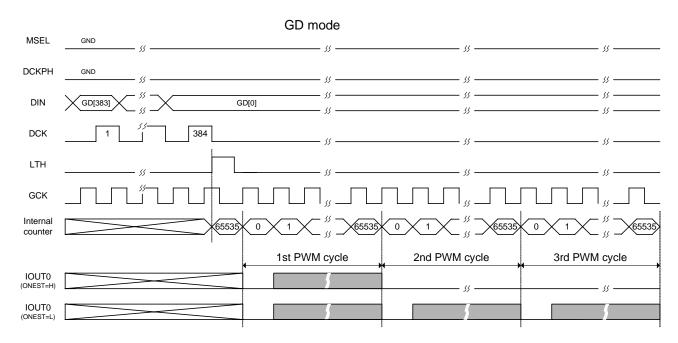

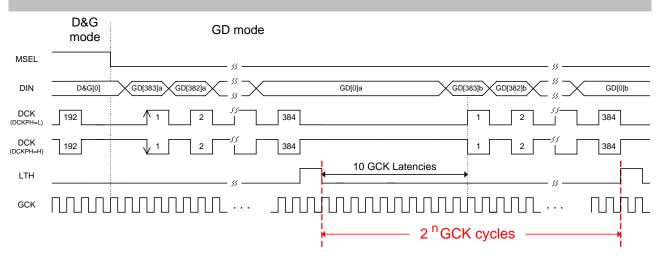

When MSEL is set to low, the DM164 enters GD mode. The internal shift registers changes to 384-bit wide. The input data can be transferred at either the rising edge of DCK or the falling edge of DCK by setting DCKPH to L or H. After all data are transferred into the GD mode shift registers, the GD mode data can be latched from shift registers to the data latches by a LTH signal at GD mode only. Figure 4 shows the GD mode data input timing chart.

Figure 4. GD Mode Data Input Timing Chart

### Thermal Alarm and Shutdown

The DM164 provides a temperature error detection circuit, when EN\_B=H and the junction temperature of the IC reaches about 130°C, a T130 signal will change the ALARM pin to low level. At this moment, the system should start up the fan or decrease the output currents to lower the junction temperature. If the system has not any protected circuit, the junction temperature might continue to rise. Once it reaches approximately above 170°C, a T170 signal and a Shutdown signal will cause the driver to shutdown all the outputs, the ALARM pin remains in low level. Basically, the IC will cool down and return to the safe operating temperature approximately below 130°C. When the operating temperature below 130°C, the ALARM pin will reset to high level, disable the warning, and restart all the outputs. Operation in the thermal situation for a long time may cause chip damage permanently. The thermal error signals (T130, T170, Shutdown) can be transferred out from DOUT pin.

Figure 5. Thermal Alarm and Shutdown

### **Open Detection**

If there is any one of the 24 LEDs open or disconnected, the DM164 can detect and report the error. The open detection circuit works when the following two conditions are met simultaneously:

- 1. IOUTn is on (IOUTn > 200ns and EN\_B="L").

- 2. When the output voltage at IOUTn is less than 0.2 V

The open error signal (OPE) has two methods to communicate the error signals to the system. One is through serial output data to indicate which channel has failure (OPEn=H => IOUTn is open). The other is by means of dedicated Alarm pin when EN\_B=L.

### **Status Information Output**

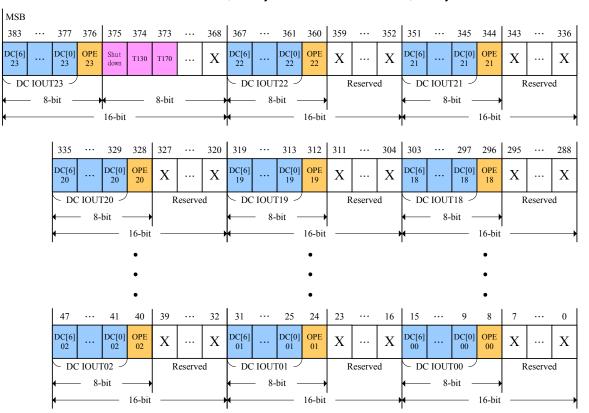

When the DM164 operates at GD mode, after the LTH signal latches the input data from shift registers to the data latches, the shift registers data will be replaced by the status information. The status information includes the thermal error signals (Shutdown, T130 and T170,), open error signals (OPE) and dot correction data (DC), which will be transferred out from DOUT pin. Figure 6 shows the status information format.

(a. IOUT shut down => Shut down=L, b. Tj>130 $^{\circ}$ C => T130=H, c. Tj>170 $^{\circ}$ C => T170=H)

Figure 6. Status Information Data Format (ER[383:0])

In order to catch correct open error signals. DCK must wait for at least 10 GCK latencies after the LTH signal latches the input data. Figure 7 shows the timing chart.

Figure 7. Open Error Signals Timing Chart

## IOUT Delay & EN\_B Delay

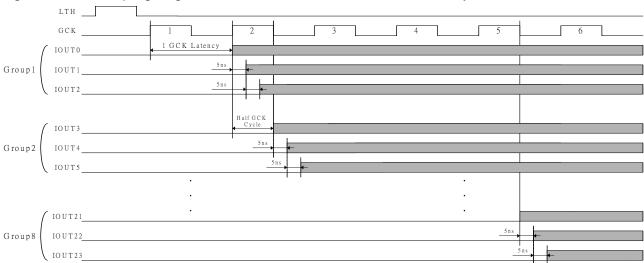

The DM164 provides delay circuits between IOUTs. All IOUTs are divided into eight groups and every three outputs of different colors form a group. For example, IOUT0 IOUT1 and IOUT2 form the group1; IOUT3 IOUT4 and IOUT5 form the group2. The delay time between every group is half GCK cycle time. Each IOUT delay in the same group is 5ns (typical). Figure 8 shows the IOUT delay timing chart. Besides the iout delay, the EN\_B is also associated with GKC signal. When EN\_B goes high and GCK keeps going, then each group of IOUTs will turn off one by one depending on the GCK sequence. If EN\_B goes high but GCK stops going, then the IOUTs will not turn off normally.

Figure 8. IOUT Delay Timing Chart

# lout Delay & EN\_B Delay Waveform

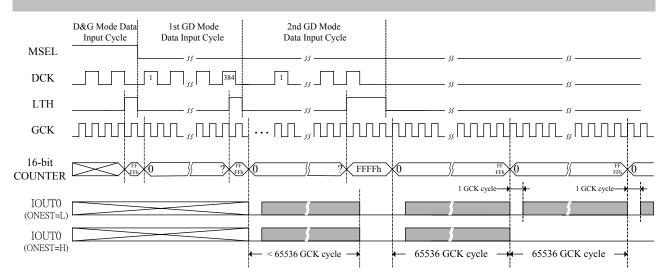

### **One-Shot Option**

The DM164 provides an option that users can make the output turn on for just a PWM cycle time, i.e. in the GD mode, after a LTH signal, the output only turn on for 65536  $T_{GCK}$  time. After 65536  $T_{GCK}$ , the output will automatically turn off. This is called One-Shot function. Figure 9 shows the difference between One-Shot or not. When ONEST = H, one-shot function is enabled. The output will just turn on at  $1_{st}$  PWM cycle. When ONEST = L, one-shot function is disabled. The output will repeat at every PWM cycle.

Figure 9. One-Shot Operation

### Grayscale PWM Operation

When DCKPH=L, the grayscale PWM cycle starts with the falling edge of LTH (see Figure 10). A LTH = H signal will set the 16-bit PWM counter value to FFFFh. The first GCK pulse after LTH increases the PWM counter by one and switches on all IOUT with grayscales value not zero. Each following rising edge of GCK increases the PWM counter by one. The DM164 compare the grayscale PWM value of each output IOUT with grayscale counter value. If the grayscale PWM value is larger than grayscale counter value, the IOUT will switch on.

Figure 10. Grayscale PWM Operation

### **Maximum Output Current**

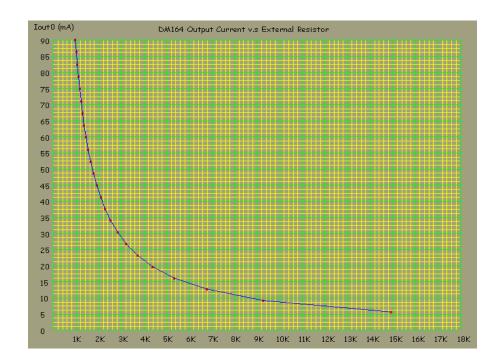

The maximum output current is set by an external resistor. The resistor is connected between Rext and GND. Varying the resistor value can adjust the current scale ranging from 5mA to 90mA. The reference voltage of REXT terminal (Vrext) is approximately 1.23V. The maximum output current (I<sub>max</sub>) value can be calculated roughly by the following equation:

$$Imax \cong \frac{Vrext (V)}{Rrext (\Omega)} \times 64$$

where:

Vrext = 1.23V

Rrext = external resistor.

### **Global Brightness Control**

The global brightness control function can adjust the global current of each color independently. The output current ( $I_{global}$ ) can be adjusted in 256 steps from ((1/256)\*100)% to 100% of the maximum output current. The following equation can calculate the global brightness control current ( $I_{global}$ )

$$Iglobal \cong \frac{GB+1}{256} \times Imax$$

where:

$I_{max}$  = the maximum output current.

GB = the global brightness control value for different colors.

### **Dot Correction**

Besides global brightness control, the DM164 also has the capability to adjust the output current of each channel IOUT00 to IOUT23 independently. The output current ( $I_{dot}$ ) can be adjusted in 128 steps from ((1/128)\*100) % to 100% of the global brightness control current. The following equation can calculate the dot correction current ( $I_{dot}$ )

$$Idot \;\cong\; \frac{DC+1}{128} \;\times\; Iglobal \;\cong\; \frac{DC+1}{128} \;\times\; \frac{GB+1}{256} \;\times\; Imax$$

where:

$I_{global}$  = the global brightness control current

DC = the dot correction value for each output.

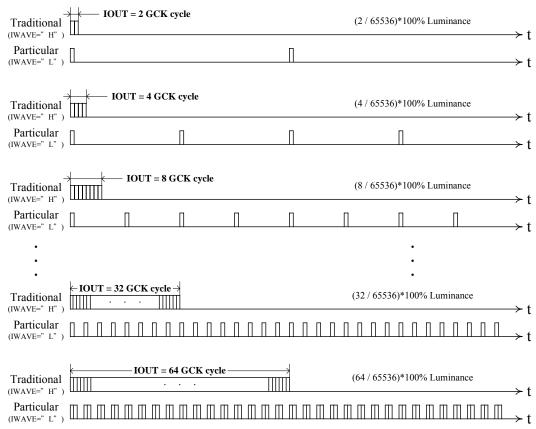

### **Average Separate IOUT Waveform**

The DM164 incorporates a different PWM counter, hence the IOUT waveform demonstrate a very different characteristics compare to conventional PWM counter. In the DM164, when IWAVE="L," the IOUT waveform is averagely divided into 32(maximum) sections. Figure 11 shows the difference between traditional IOUT waveform and particular IOUT waveform.

Figure 11. Average Separate IOUT Waveform

# **Output Current vs. External Resistor**

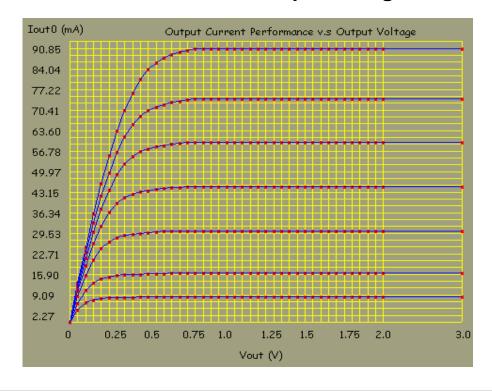

# **Output Current Performance vs. Output Voltage**

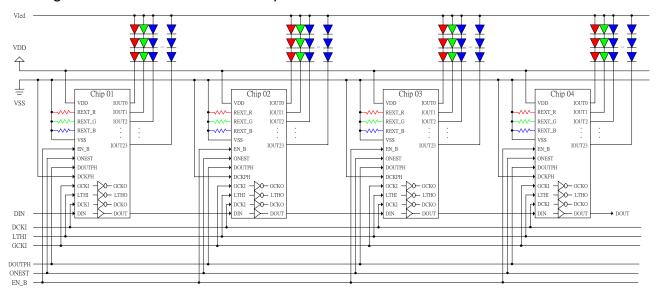

### **Application Diagram**

- a) DCK LTH and GCK signals: Global Connected

- \* Each DCKPH input pin of all chips should be connected to the same voltage level. Figure 12 shows that all DCKPH pins are connected to VSS.

Figure 12. DCK LTH and GCK signals: Global Connected

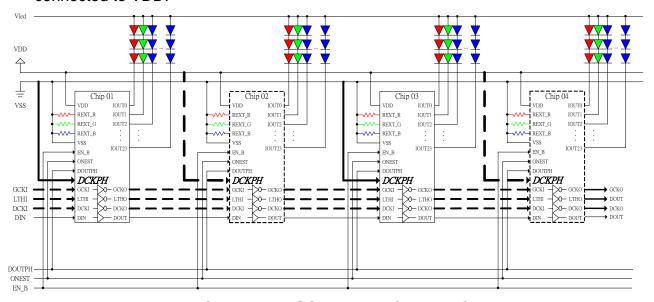

- b) DCK LTH and GCK signals: Cascade Connected

- \* DCKPH input pins of odd stages (Chip01, Chip03...) and even stages (Chip02, Chip04...) should be connected to different voltage level. Figure 13 shows that CLKPH pins of odd stages are connected to VSS, and CLKPH pins of even stages are connected to VDD.

Figure 13. DCK LTH and GCK signals: Cascade Connected

- c) Less Than 16-bit PWM Grayscale Application

- c.1 IWAVE="H" and less than 16-bit PWM application

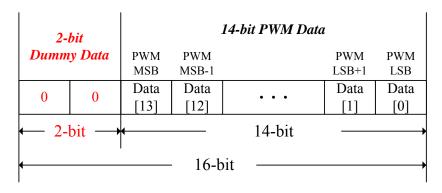

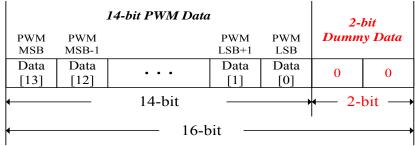

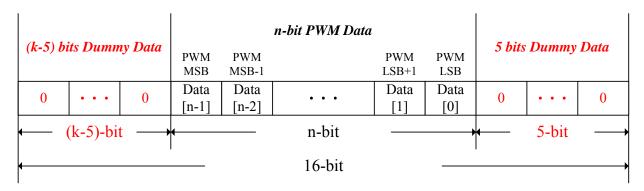

When the DM164 operates at n-bit PWM grayscale application and IWAVE is set to "H" (where n is less than 16). Users must add k-bit dummy data into the 16-bit GD mode data of each channel (where k = 16-n). The 16-bit GD mode data format of each channel is showed below:

| k-bit Dummy Data |       |   | PWM<br>MSB    | PWM<br>MSB-1  | n-bit PWM Data | PWM<br>LSB+1 | PWM<br>LSB  |

|------------------|-------|---|---------------|---------------|----------------|--------------|-------------|

| 0                | • • • | 0 | Data<br>[n-1] | Data<br>[n-2] | • • •          | Data<br>[1]  | Data<br>[0] |

| •                | k-bit |   | •             |               | n-bit          | _            | •           |

| •                |       |   |               | 16-bit        |                |              |             |

The k-bit MSB of 16-bit GD mode data of each channel must be filled with all "0" (k=16-n). For example:

When the DM164 operates at 14-bit PWM grayscale application and IWAVE="H", the 2-bit MSB of the 16-bit GD mode data must be filled with "0". The 16-bit data format is showed below:

Figure 14 shows the timing diagram when the DM164 operates at n-bit PWM grayscale application. The frame cycle of n-bit PWM grayscale application can be controlled by GCK and LTH signals.

Figure 14. Operating at n-bit PWM Grayscale Application Timing Diagram

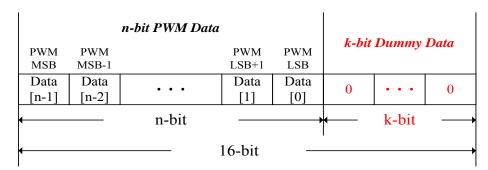

### c.2 IWAVE="L" and 11~15-bit PWM application

When the DM164 operates at n-bit PWM grayscale application and IWAVE is set to "L" (where n is between  $11\sim15$ ). Users must add k-bit dummy data into the 16-bit GD mode data of each channel (where k=16-n). The 16-bit GD mode data format of each channel is showed below:

The k-bit LSB of 16-bit GD mode data of each channel must be filled with all "0" ( k=16-n & k < 6).

### For example:

When the DM164 operates at 14-bit PWM grayscale application and IWAVE="L", the 2-bit LSB of the 16-bit GD mode data must be filled with "0". The 16-bit data format is showed below:

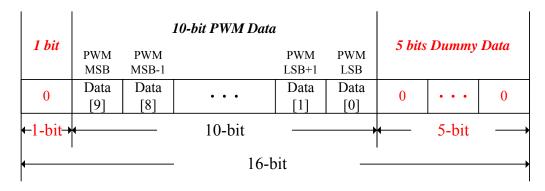

### c.3 IWAVE="L" and Less than 11-bit PWM application

When the DM164 operates at n-bit PWM grayscale application and IWAVE is set to "L" (where n is less than 11). Users must add k-bit dummy data into the 16-bit GD mode data of each channel (where k = 16-n). The 16-bit GD mode data format of each channel is showed below:

The 5 bits LSB and (k-5) bits MSB of 16-bit GD mode data of each channel must be filled with all "0" (k=16-n & k > 5).

### For example:

When the DM164 operates at 10-bit PWM grayscale application and IWAVE="L", the 5-bit LSB and 1-bit MSB of the 16-bit GD mode data must be filled with "0". The 16-bit data format is showed below:

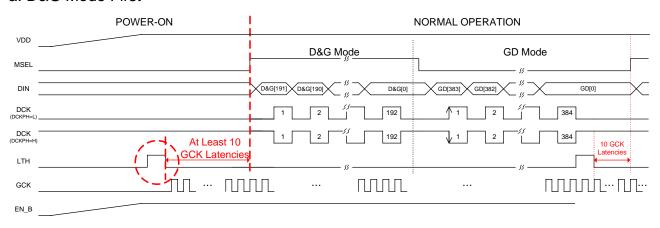

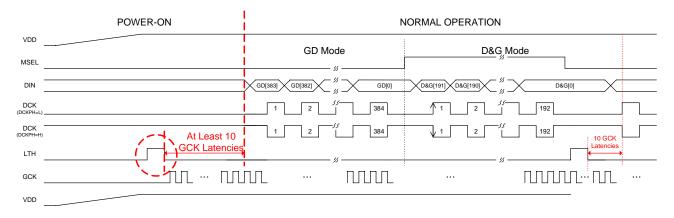

### d) Power-on Reset Suggestion

The DM164 doesn't built-in automatic power-on reset function. In order to make sure the DM164 can work normally after the power-on situation. Users can add an LTH pulse before normal operation, like Figure 15 shows.

### a. D&G Mode First

### b. GD Mode First

Figure 15. Power-on Reset Suggestion Timing Diagram

### **Power Dissipation**

The power dissipation of a semiconductor chip is limited to its package and ambient temperature, in which the device requires the maximum output current calculated for given operating conditions. The maximum allowable power consumption can be calculated by the following equation:

$$Pd(max)(Watt) = \frac{Tj(junction\ temperature)(max)(\ C) - Ta(ambient\ temperature)(\ C)}{Rth(junction-to-air\ thermal\ resistance)(\ C/Watt)}$$

The relationship between power dissipation and operating temperature can be refer to the figure below:

Based on the Pd(max), the maximum allowable voltage of output terminal can be determined by the following equation:

Vout0 x Iout0 x Duty0 + . . . + Vout23 x Iout23 x Duty23 < Pd(max) - VDD x IDD

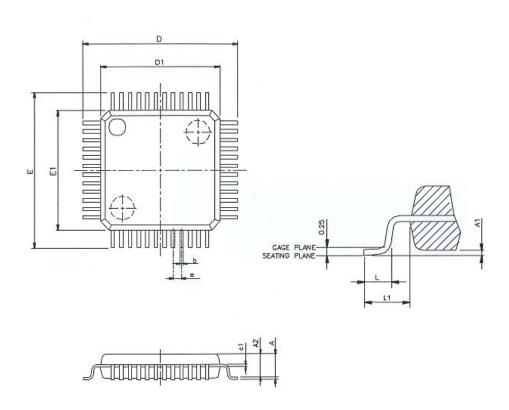

# **Package Outline Dimension**

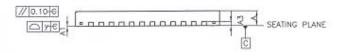

# LQFP48

| LQFP48 - DIMENSION (mm) |           |      |       |        |               |      |       |  |

|-------------------------|-----------|------|-------|--------|---------------|------|-------|--|

| SYMBOL                  | MIN.      | NOM. | MAX.  | SYMBOL | MIN.          | NOM. | MAX.  |  |

| А                       | -         | -    | 1.600 | E      | 9.000 BSC     |      |       |  |

| A1                      | 0.050     | -    | 0.150 | E1     | 7.000 BSC     |      |       |  |

| A2                      | 1.350     | -    | 1.450 | е      | 0.500 BSC     |      |       |  |

| c1                      | 0.090     | -    | 0.160 | b      | 0.170         | -    | 0.270 |  |

| D                       | 9.000 BSC |      |       | L      | 0.450 - 0.750 |      | 0.750 |  |

| D1                      | 7.000 BSC |      |       | L1     | 1.000 REF     |      |       |  |

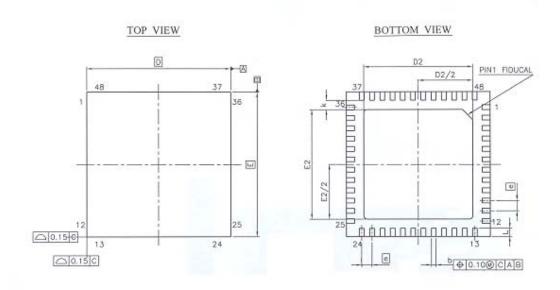

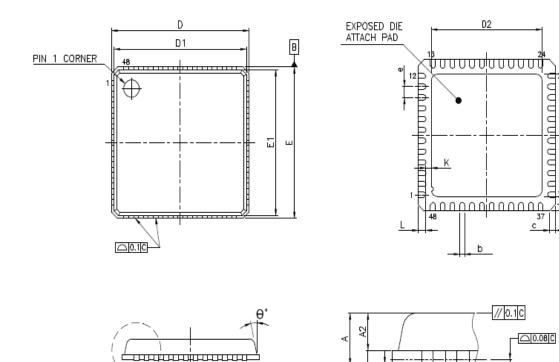

# QFN48-Saw Type

| QFN48 - DIMENSION (mm) |                   |       |       |        |                  |       |          |  |  |

|------------------------|-------------------|-------|-------|--------|------------------|-------|----------|--|--|

| SYMBOL                 | MIN.              | NOM.  | MAX.  | SYMBOL | MIN.             | NOM.  | MAX.     |  |  |

| А                      | 0.700 0.750 0.800 |       |       | E      | 7.000 BSC        |       |          |  |  |

| A1                     | 0.000             | 0.020 | 0.050 | E2     | 5.100            | 5.200 | 5.300    |  |  |

| A3                     | 0.203 REF         |       |       | е      | 0.500 BSC.       |       |          |  |  |

| b                      | 0.180             | 0.250 | 0.300 | k      | 0.200            | -     | <u>-</u> |  |  |

| D                      | 7.000 BSC         |       |       | L      | 0.300 0.400 0.50 |       | 0.500    |  |  |

| D2                     | 5.100 5.200 5.300 |       |       | у      | 0.080            |       |          |  |  |

# QFN48- Punch Type

| QFN48 - DIMENSION (mm) |                   |       |       |        |           |       |        |  |  |

|------------------------|-------------------|-------|-------|--------|-----------|-------|--------|--|--|

| SYMBOL                 | MIN.              | NOM.  | MAX.  | SYMBOL | MIN.      | NOM.  | MAX.   |  |  |

| А                      | 0.800             | 0.850 | 0.900 | D2     | 4.900     | 5.100 | 5.300  |  |  |

| A1                     | 0.000             | 0.020 | 0.050 | E      | 6.900     | 7.000 | 7.100  |  |  |

| A2                     | 0.650 REF         |       |       | E1     | 6.650     | 6.750 | 6.850  |  |  |

| А3                     | 0.203 REF         |       |       | E2     | 4.900     | 5.100 | 5.300  |  |  |

| b                      | 0.180 0.250 0.300 |       |       | е      | 0.500 BSC |       |        |  |  |

| С                      | 0.240             | 0.420 | 0.600 | К      | 0.200     | -     | -      |  |  |

| D                      | 6.900             | 7.000 | 7.100 | L      | 0.300     | 0.400 | 0.500  |  |  |

| D1                     | 6.650             | 6.750 | 6.850 | θ ο    | 0.000     | -     | 12.000 |  |  |

(A3)

DETAIL A

C SEATING PLANE

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.

Silicon Touch Technology, Inc. reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.